wróć do opisu Tiny DDS

wróć do opisu Tiny DDS |

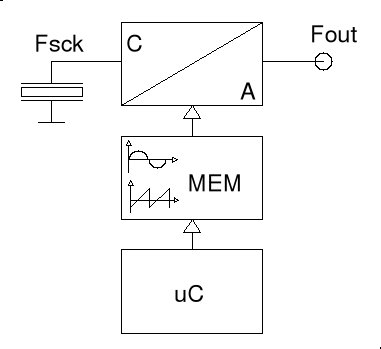

Podany niżej opis działania DDS jest możliwie prostym przedstawieniem zasady działania tego typu urządzeń z zastosowaniem daleko idących uproszczeń. Główne bloki funkcjonalne DDS to przetwornik cyfrowo- analogowy oraz pamięć, w której przechowywane są dane dotyczące generowanego przebiegu. Aby system DDS mógł działać potrzebne jest jeszcze zródło częstotliwości wzorcowej oznaczone jako Fsck oraz mikrokontroler, który jest w stanie wysterować układ DDS.  Blok funkcjonalny pamięci zawiera dane jakie przetwornik cyfrowo- analogowy wykorzystuje do odtworzenia kształtu generowanego przebiegu. Oczywiście generowany przebieg może mieć dowolny kształt, symbolicznie zaznaczono, że może to być na przykład sinusoidalny lub piła. Dokładność odtworzenia zaprogramowanego w pamięci przebiegu jest bardzo duża. Układy AD98xx mają pamięć zawierającą teoretycznie 2^32 wartości co wyraża się liczbą 4 294 967 296 wartości składających się na odtworzenie jednego okresu generowanego przebiegu. Dla pełnej rozdzielczości przetwornik cyfrowo- analogowy pobudzany impulsami zegara wzorca Fsck ustawia na wyjściu Fout napięcie odpowiadające kolejnym wartościom z tablicy pamięci dla wybranego kształtu przebiegu. Poziom napięcia na wyjściu zmienia się z prędkością taktowania Fsck i dla przykładu dla układu AD9835 może się to odbywać z częstotliwością maksymalną 50MHz. Zakładając, że wykorzystamy pełną rozdzielczość układu można powiedzieć, że aby odtworzyć przebieg o 2^32 poziomach z prędkością 50MHz trzeba 2^32/50MHz = 85,89934592 sekund. Odwrotność tej liczby to oczywiście najniższa możliwa do wygenerowania częstotliwość w tych warunkach. Jeśli jednak zamiast każdej wartości z pamięci wykorzysta się co setną wtedy do dyspozycji będzie 2^32/100 stanów czyli 42949673 a pełne odtworzenie przebiegu nastąpi w czasie stukrotnie krótszym czyli ok. 0.86 sek co w przeliczeniu na czestotliwość wynosi ok. 1.16Hz. Idąc dalej, jeśli do budowy sygnału wyjściowego użyjemy co milionowego stanu z pamięci uzyskamy częstotliwość 11642Hz. Wydawać się może, że co milonowy stan z pamięci to zbyt mało ale należy pamiętać, że korzystamy ciągle z 2^32/1000000= 4295 stanów na odtworzenie jednego okresu generowanego przebiegu. Teoria przewiduje, że do odtworzenia sygnału wystarczą 2 próbki sygnału w okresie więc i tak jest to znacznie więcej niż trzeba. W praktyce możliwe jest uzyskanie na wyjściu częstotliwości nie wyższej niż ok. połowa częstotliwości zegara Fsck. Dla układów AD9835 pożądaną częstotliwość uzyskuje się przez wprowadzenie do układu DDS wartości liczbowej liczonej następująco:

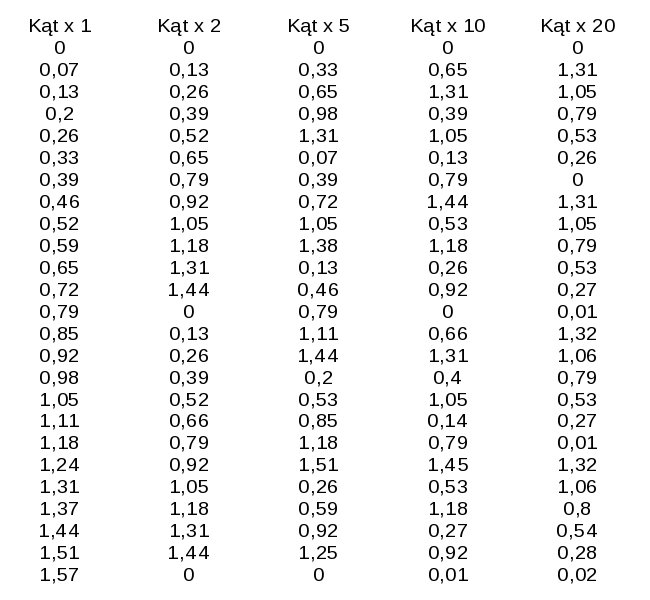

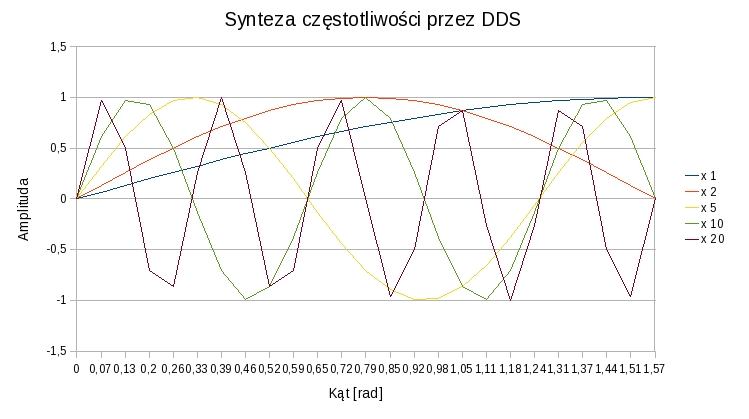

Aby przybliżyć proces tworzenia sygnału przez układ DDS załóżmy, że do utworzenia mamy sygnał sinusoidalny opisany wartościami argumentów z pierwszej kolumny wyrażonych w radianach. Pokazane w pierwszej kolumnie wartości odpowiadają kątom od 0 do 90 stopni (wyrażonym w radianach - kąt pełny 360 stopni ma 2*pi radianów co wynosi ok. 6.28) w 24 krokach a więc pełnej ćwiatce przebiegu sinusoidalnego i można uznać je za komplet argumentów opisujących przebieg sinusoidalny w tablicy pamięci na podstawie których na wyjściu uzyskuje się napięciu o wartości sin(alfa). Kolejne trzy dalsze ćwiartki jednego okresu są identyczne tylko odbite lustrzanie względem osi X lub Y. W przykładzie założono, że pełna tablica argumentów zawiera 24 wartości kąta a odpowiadający im wykres sin(alfa) na rysunku to przebieg pierwszej ćwiartki sinusoidy złożony ze wszystkich kolejnych wartości sin(alfa) dla wszystkich 24 wartości kąta.  W kolejnych kolumnach zestawienia pokazano wartości kąta odpowiadające wyborowi z pierwszej kolumny danych co 2, co 5, co 10 i co 20 argument (liczone modulo 2*pi). Przebiegi dla co 2 i co 5 wartości z tablicy są jeszcze dość gładkie ale ich wykresy mają oczywiście częstotliwości 2 i 5 krotnie większe od częstotliwości podstawowej. Dla wyboru co 10 a szczególnie dla wyboru co 20 wartość z tabeli pamięci widać wyrażnie, że częstotliwość wprawdzie zwiększa się 10 i 20 krotnie ale kształt przebiegu nie jest już gładki i w widmie tych sygnałów pojawią się wyższe harmoniczne podczas obserwacji na analizatorze widma. Te niepożadane składowe z reguły usuwa się stosując na wyjściu układu DDS filtry dolnoprzepustowe. Podany wyżej opis jest w wielu punktach uproszczony. W rzeczywistych układach ilość wartości zakodowanych w pamięci rzadko przekracza 2^16 lub 2^20 bo nie jest potrzebna większa dokładność ze względu na nierozróżnialność sąsiednich stanów, układy DDS mogą zawierać oprócz wyjścia częstotliwości podstawowej także wyjście generujące od razu przebieg piłokształtny skorelowany z generowanym przebiegiem sinusoidalnym a dodatkowo, oprócz częstotliwości można także zmieniać fazę sygnału co jest bardzo przydatne w konstruowaniu koderów i dekoderów.. |

wróć do opisu Tiny DDS |